混合信号模数转换(ADC)CMOS集成电路设计是连接物理世界与数字世界的关键桥梁,它将模拟信号(如声音、温度、压力)精确地转换为数字信号,以供后续的数字系统处理。而高效的数据处理和存储服务则是释放这些数字信号价值的核心环节。本文将探讨混合信号ADC CMOS集成电路的设计要点,并阐述其在现代数据处理与存储服务生态系统中的关键作用。

一、混合信号ADC CMOS集成电路设计核心

混合信号ADC设计在单一的CMOS芯片上集成了模拟和数字电路,面临着功耗、精度、速度与面积等多重挑战。其主要设计考量包括:

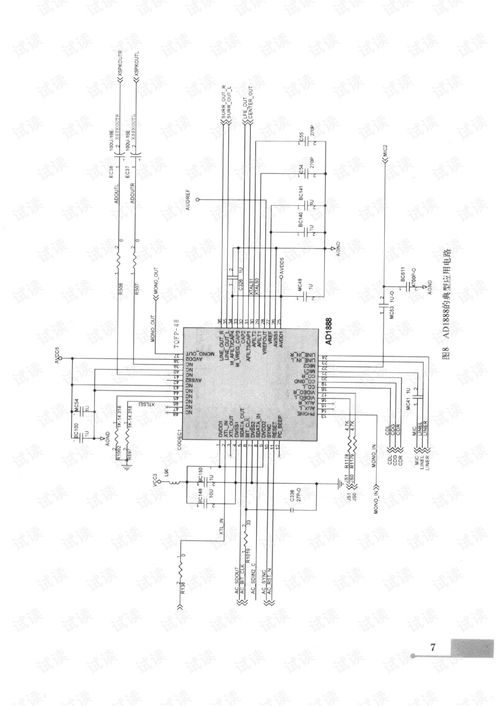

- 架构选择:根据应用需求(如高精度、高速或低功耗),选择合适的ADC架构,如逐次逼近型(SAR)、流水线型(Pipeline)、Sigma-Delta型等。SAR ADC因其结构简单、功耗低,在中等精度和速度的应用中(如传感器接口)备受青睐。

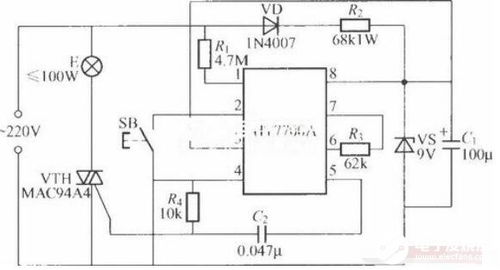

- 模拟前端设计:这是设计的核心难点,包括采样保持电路、比较器、基准电压源等。设计需克服CMOS工艺中器件失配、噪声(热噪声、1/f噪声)和非线性等因素,确保采样的准确性和线性度。

- 数字校准与处理:现代高性能ADC广泛集成数字校准电路(如后台校准),以校正模拟电路的增益误差、失调和非线性,显著提升整体性能。数字部分还包括控制逻辑和数字接口。

- 低功耗设计:针对物联网、可穿戴设备等电池供电场景,需采用低电压设计、电源门控、动态偏置等技术来优化功耗。

- 工艺与封装:先进的CMOS工艺(如28nm、16nm及以下)有助于提高集成度、降低功耗,但给模拟设计带来更大挑战。封装需考虑信号完整性和热管理。

二、从ADC输出到数据价值:处理与存储服务链

高性能ADC产生的原始数字数据流,必须经过一系列高效的处理与存储,才能转化为可用的信息和洞察。这一服务链通常包括:

- 前端数据处理:在靠近ADC的本地(如微控制器、FPGA或专用ASIC)进行实时预处理,包括数字滤波、降噪、数据压缩、特征提取等。这能有效减少需上传的数据量,降低系统延迟和功耗。例如,在图像传感器中,ISP(图像信号处理器)对ADC输出的原始数据进行处理以生成高质量图像。

- 数据传输:处理后的数据通过有线(如以太网)或无线(如5G、Wi-Fi、低功耗广域网)接口传输至云端或边缘服务器。高速ADC(如用于5G射频的ADC)产生的海量数据对传输带宽提出了极高要求。

- 云端/边缘数据处理与分析:在数据中心或边缘节点,运用强大的计算资源进行更复杂的分析,如大数据分析、机器学习和人工智能模型推理。例如,工业设备中ADC采集的振动信号经云端分析,可实现对设备健康状况的预测性维护。

- 数据存储与管理服务:处理结果和原始数据(如需)被存入数据库或数据湖。现代存储服务提供高可靠性、可扩展性和安全性,支持结构化、半结构化和非结构化数据。数据管理服务包括编目、生命周期管理(冷热数据分层)和快速检索。

- 应用与服务集成:处理后的信息被集成到具体的应用程序和服务中,如监控仪表板、自动化控制指令、用户报告或触发告警,完成从物理信号到商业或操作决策的价值闭环。

三、协同设计与未来趋势

ADC芯片设计与数据处理存储服务正日益紧密地协同进化:

- 智能ADC与存算一体:未来的ADC可能集成更多预处理智能(如事件驱动采样、稀疏化编码),直接输出更有意义的数据,减轻后端负担。存算一体架构探索在存储器内进行计算,有望打破“冯·诺依曼瓶颈”,特别适合ADC产生的大数据流处理。

- 面向应用的定制化:针对自动驾驶(激光雷达/毫米波雷达)、科学仪器、医疗影像等特定领域,ADC设计与后端处理算法(如压缩感知、神经网络)联合优化,实现系统级性能最优。

- 安全与隐私:从ADC端开始考虑数据安全(如硬件加密),确保在传输和存储过程中的隐私保护,变得愈发重要。

结论

混合信号CMOS ADC集成电路设计是数据采集的源头,其性能直接决定了数字世界的“感官”精度。而强大、高效的数据处理与存储服务则是消化这些数据、提炼核心价值的“大脑”与“记忆”。两者相辅相成,共同构成了从物理感知到智能决策的完整技术链条,驱动着物联网、人工智能、工业4.0和科学探索等众多领域的持续创新。随着工艺进步和架构革新,这一链条将变得更加高效、智能和紧密集成。