专用集成电路(ASIC)设计是当代电子工程与半导体产业的核心领域之一,它专注于为特定应用定制高性能、低功耗的集成电路解决方案。本教程旨在提供一份实用的入门指南,帮助读者理解ASIC设计的基本流程、关键技术和实际应用。

一、ASIC设计概述

专用集成电路(ASIC)与通用集成电路(如微处理器)不同,它是为特定功能或系统量身定制的芯片,广泛应用于通信、消费电子、汽车电子、医疗设备等领域。ASIC设计涉及从概念到物理实现的完整过程,包括需求分析、架构设计、逻辑实现、物理布局、验证和测试等环节。其优势在于优化性能、降低功耗和成本,但开发周期较长且初始投资较高。

二、设计流程与阶段

ASIC设计通常遵循标准化的流程,主要分为以下几个阶段:

- 需求分析与规范定义:明确芯片的功能、性能指标(如速度、功耗、面积)和接口要求,编写详细的设计规范文档。

- 架构设计:根据规范,确定芯片的整体结构,包括模块划分、数据流控制、时钟和电源管理策略等。

- 逻辑设计:使用硬件描述语言(如Verilog或VHDL)进行寄存器传输级(RTL)编码,实现功能逻辑。此阶段注重代码的可综合性和可验证性。

- 功能验证:通过仿真和形式验证方法,确保RTL设计符合规范。常用工具包括仿真器(如ModelSim)和验证语言(如SystemVerilog)。

- 综合与优化:将RTL代码转换为门级网表,并利用约束(如时序、面积)进行逻辑优化,生成初步的物理设计基础。

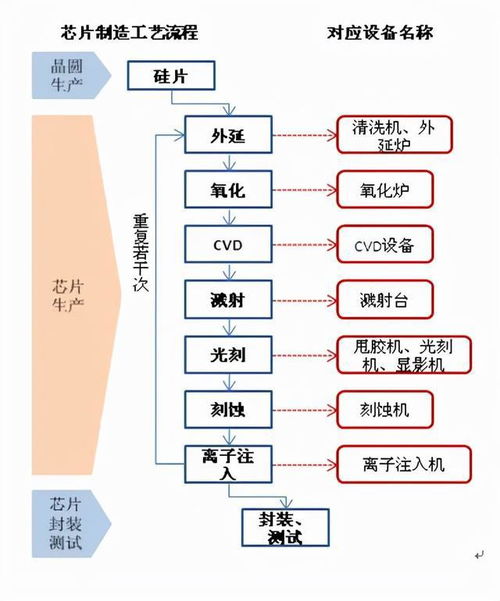

- 物理设计:包括布局规划、时钟树综合、布线、寄生参数提取和时序分析等步骤,确保芯片满足制造要求。工具如Cadence Innovus或Synopsys IC Compiler被广泛使用。

- 验证与签核:进行物理验证(如DRC、LVS)和时序签核,确保设计无误后,生成GDSII文件交付给晶圆厂。

- 测试与量产:设计测试向量,进行芯片测试和故障分析,最终实现批量生产。

三、关键技术要点

- 低功耗设计:随着移动设备和物联网的普及,功耗成为关键指标。技术包括电源门控、多电压域、动态电压频率调整(DVFS)等。

- 时序收敛:在高性能设计中,时钟偏移和路径延迟必须严格控制,通过优化时钟树和约束管理来实现。

- 可制造性设计(DFM):考虑工艺变异和缺陷,提高芯片良率,涉及规则调整和冗余设计。

- 验证方法学:采用基于UVM(通用验证方法学)的验证环境,提升验证效率和覆盖率。

四、实用工具与资源

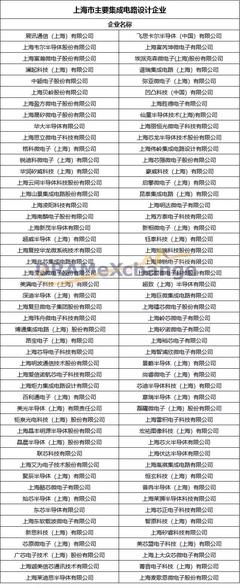

ASIC设计依赖专业软件工具链,主流供应商包括Cadence、Synopsys和Mentor Graphics(现为Siemens EDA)。初学者可以从开源工具(如Yosys用于综合)和在线课程入手,同时参考行业标准文档(如IEEE标准)和实际案例。

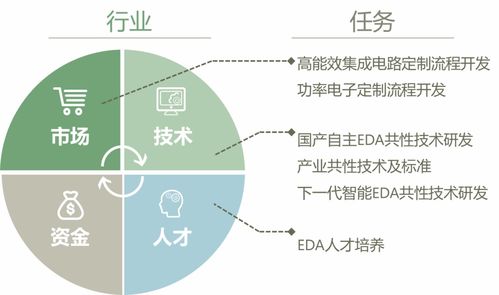

五、发展趋势与挑战

未来ASIC设计将面临工艺节点不断缩小(如3nm以下)、异构集成(如Chiplet技术)和人工智能驱动的自动化设计等趋势。挑战包括设计复杂性增加、成本上升和人才短缺,因此持续学习和实践至关重要。

###

专用集成电路设计是一个多学科交叉的领域,要求工程师具备扎实的电子学基础、编程技能和系统思维。通过本教程,希望读者能建立起ASIC设计的整体框架,并进一步探索实际项目,从而在快速发展的半导体行业中立足。建议结合具体设计工具和实验,加深对理论知识的理解,最终实现从理论到实践的跨越。